Quartus 与 Vivado 资源对比

Main

同样的程序运行在 Vivado 和运行在 Quartus 下,最后得到的 utilization 格式不同,该如何对比他们的性能差异呢。

这里使用 Equivalent Logic Elements Used 这样一个中间值格式,最后统一成这样一个公式

1 | ELE = CLB_LUT * 2.18 = ALM * 2.95 |

接下来解释下为什么是这两个值。

查看 Intel 和 AMD 两家 FPGA 芯片手册,可以发现自家在对比不同系列芯片包含资源时,都会使用一个 Logic Element 值来归一化。对于 AMD 而言是 System Logic Cells (K),对于 Intel 则是 Logic elements (LEs)。

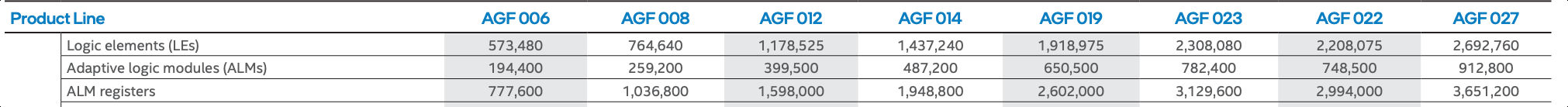

如下截图简单看下,具体请参考下方链接

a. Intel

Link : https://cdrdv2-public.intel.com/730595/Intel-fpga-product-catalog-23.1.pdf

上图中例子是 Intel Agilex7 不同 Family 的 resource 对比,可以看到 LEs/ALMs 基本都是 2.95。依次这样计算可以得到如下比例:

- Stratix V and Arria 10 : 1 ALM = 2.65 Logic elements

- Stratix 10 and Agilex : 1 ALM = 2.95 Logic elements

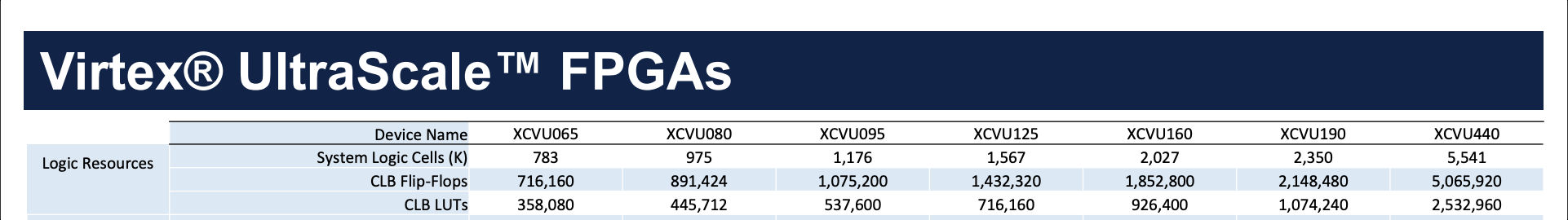

b. AMD

Link: ultrascale-fpga-product-selection-guide.pdf • Viewer • AMD Adaptive Computing Documentation Portal (xilinx.com)

上图中例子是 AMD Virtex UltraScale 不同 Family 的 resource 对比,可以看到 CLB_LUTs/System Logic Cells 基本都是 2.18,而且对比其他系列可以发现比例都是相同的,即

- UltraScale and UltraScale+ : 1 CLB_LUT = 2.18 System Logic Cells

c. Logic Cells to System Logic Cells

Xilinx 在 2014 年时候推出的 UltraScale 架构中引入了新的逻辑单元计数方式,从 Logic Cells 转变为了 System Logic Cells。这个变化并没有改变芯片本身的实际规模,只是改变了计数方式。事实上,这种举措看上去更像是商业营销的一种手段,参考链接 2 中评论,提到这个名称改变带来的变化

However, if you look back at the NEW Xilinx product tables, you’ll find that same old XCVU065 650K device now expanded into a 783K device, thanks to the magic of “System Logic Cells”.

根据这里的参数,改变后 System Logic Cells 大小差不多是原先 Logic Cells 的 1.2 倍。(找不到官方手册具体参数了)

d. Summary

综上,回到最开始的结论,如果想要统一两个厂家之间芯片资源的话,使用如下公式即可

1 | ELE = CLB_LUT * 2.1875 = ALM * 2.95 |